AD9288数据手册理解

AD9288 是一个双通道的8位高速ADC芯片,最高采样里100M,两个通道可以组合成一个200M的单通道ADC

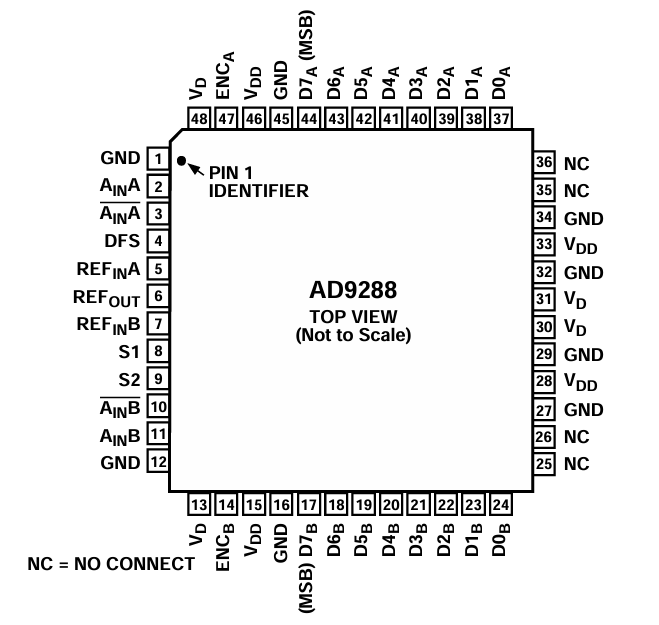

引脚说明

AINA 和 AINA# 通道A差分输入AINB 和 AINB# 通道B差分输入DFS 数据输出格式选择,0:二进制输出,1:补码输出REFOUT 参考电压输出,1.25V (1.2V - 1.3V)REFINA、REFINB 两个通道的参考电压输入,与REFOUT引脚短接再接个0.1uF对地电容S1、S2 ADC工作模式切换,见下表ENCA、ENCB 时钟输入信号D0A - D7A、D0B - D7B ADC采集数据并口输入,输出数据与采样点间隔4个时钟信号VD 模拟地VDD 数字地GND 地

工作模式说明

S1 和 S2 的电平决定芯片的工作模式

| S1 | S2 | 说明 |

|---|---|---|

| 0 | 0 | 通道A和通道B均休眠 |

| 0 | 1 | 通道A工作,通道B均休眠 |

| 1 | 0 | 通道A、通道B都工作 |

| 1 | 1 | 通道A、通道B都工作,且通道B的数据输出延迟半个周期 |

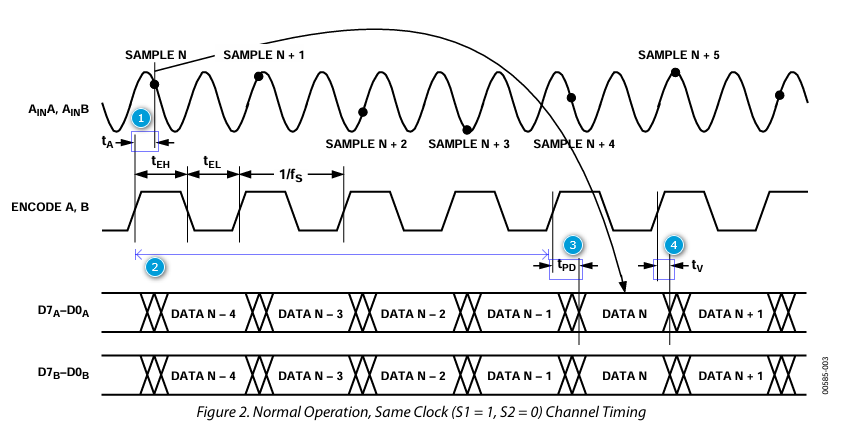

模式2和模式3时序图

- 时钟上升沿TA时间过后开始采样

- 经过四个周期之后数据采样完毕

- 第四个周期的上升沿TPD之后数据准备完毕,可以读取

- 第五个周期的上升沿TV之后,数据开始切换为下一个采样点的数据

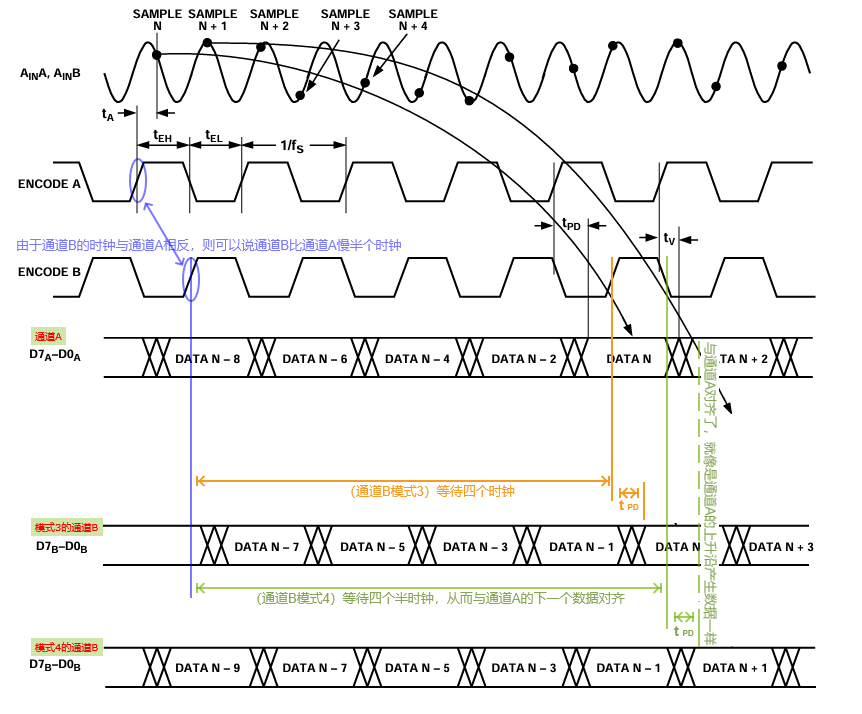

模式4时序图

模式4是给合并双通道准备的,为了实现双通道合并,则需要错开采样时间,即时钟A和时钟B的相位要间隔180度(或者说时钟A和时钟B的波形需要相反、通道B的时钟要比通道A晚半个周期)

在时钟错开的情况下,通道A和通道B的数据输出时间也是错开的,不便于单片机读取数据,所以模式4就把通道B的数据输出延迟半个周期

模式3和模式4 在 通道A和通道B的时钟相反时的数据区别